### A Survey of Power Management in Embedded System Using Transistor Sizing

M. Sinduja<sup>1</sup>, G. Sathiyabama<sup>2</sup> (Department of ECE, Sathyabama University, India) (Department of ECE, Sathyabama University, India)

**ABSTRACT:** This paper describes a transistor sizing methodology for both analog and digital CMOS circuits. Various techniques are used for power optimization in CMOS VLSI circuits. Transistor sizing is one of the important techniques for the determination of circuit performance. The aim of the power optimization is to *minimize the power and power-delay product or the energy* consumption of the circuit. Thus, the main purpose of transistor sizing in CMOS VLSI circuits is to obtain the minimum power dissipation under certain performance requirements. Transistor sizing is based on different algorithms. Analysis is based on some simulation parameter like No. of transistors, power, delay, power delay product, different technologies, aspect ratio. Each of these circuits cell exhibits different power consumption, delay and area in different VLSI technology. This survey paper discusses the different algorithms for transistor sizing analog and digital CMOS circuits and that will be beneficial for the circuit designers.

*Key-Words:* Algorithm, Delay, Low Power, Optimization, *Transistor sizing.*

#### I. INTRODUCTION

Transistor size optimization is a traditional obligation in VLSI (Very Large Scale Integration) design. It is used to improve the performance of a circuit to achieve a design goal in a specific technology. This design goal can either be boosting operating speed, lowering power consumptions or lowering area requirements. Design of VLSI circuits involves tradeoff between high speed (low delay) and low power. Design requires optimum balance between delay and power, in smaller constituent circuits and also in the larger circuit. This can be achieved by careful iterative optimization of transistor sizes. In this paper, the net list of the circuit is determined by adjusting the length and width of the MOS transistors. The figure of merit depends in a complex way on the individual size of the transistors. Changing transistor sizes in a circuit often leads to surprising results, which are not easily predicted in the low power design embedded system design.

The different algorithms have been presented for transistor sizing. The reminder of the paper is organized as follows. In section [2.1] the Monte Carlo and Genetic algorithm optimize the three digital CMOS circuits and in section [2.2] annealing and ACM compact model are discussed. Then after a simple declaration of Genetic Algorithm on consuming energy for basic arithmetic circuits, the Genetic circuit optimizer is proposed in section [2.3]. In section [2.4] optimisation techniques using geometric programming are discussed. Comparison of different transistor sizing analog and digital CMOS circuits performance and results are shown in section [3] and the conclusion is presented in section [4].

### II. LITERATURE SURVEY

#### 2.1 MONTE CARLO AND GENETIC ALGORITHM

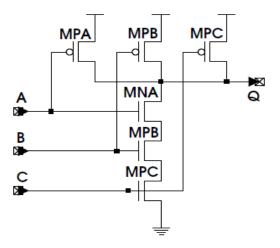

This paper [1] presents the Schoastic methods for transistor size optimization of CMOS analog and digital circuits. The performance of CMOS circuits depends on transistor sizes. The transistor sizes of digital circuits are optimized using Monte Carlo and Genetic Algorithm (GA), and also comparison is done between the two algorithms. GA is found to be more effective for larger circuits while for smaller circuits Monte Carlo optimization performs better than GA. Even nowadays, GA is one of the most used algorithms for optimization problem. This paper reviews three techniques a standard optimizer, a Monte Carlo scheme and a method based on genetic algorithms combined with very accurate spice simulations to automatically optimize transistor sizes of three digital CMOS circuits as three input NAND gate, Dynamic edge triggered DFF, Complementary pass gate full adder (CPLFA). This paper improves the performance to achieve a design goal. This design goal can either be boosting operating speed, lowering power consumption or lowering area requirements.

The Monte Carlo algorithm used in this paper results in minimum duration because the step size is first set to four times the minimum feature size and then to twice the minimum feature size and the minimum for the last third. The genetic algorithm is based on ranking selection, uniform cross over and the optimal mutation rate. In this paper the optimization of transistor sizes can be accurately performed by stochastic optimization. The paper compared four stochastic optimization methods on three CMOS subcircuits of different complexity (6, 16, 64 MOSFETS).

"Fig 2" Dynamic Edge triggered DFF

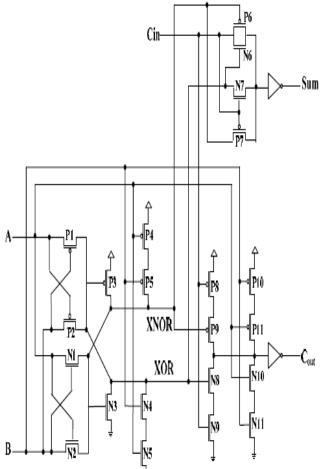

### "Fig 3" Complementary Pass Gate Full Adder (CPLFA)

On the smaller two subcircuits, the Monte Carlo method has been found to yield better results than the genetic algorithms investigated. On the largest of the three circuits, the genetic algorithms were found to yield significantly smaller variances provided they were allowed to run for a significant number of generations which suggests that the monte carlo methods tends to end up in a suboptimal solution more frequently as problem size increases.

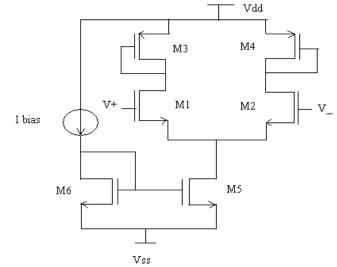

### 2.2. ANNEALING AND ACM COMPACT MODEL

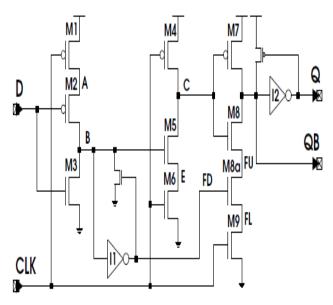

The paper [2] described a transistor sizing methodology for analog CMOS circuits that combines the physics-based gm/ID characteristics provided by the ACM compact model and the simulated annealing technique for the circuit optimization. This methodology exploits different transistor widths and lengths and provides good solutions in a reasonable CPU time, with a single technology dependent curve and accurate expressions for transconductance and current in all operation regions. The advantage of constraining the optimization within a power budget is of great importance for the designer. The optimization results obtained for the design of a two-stage operational amplifier. This paper discussed a methodology for analog design automation that combines the simulated annealing optimization technique, a physics-based transconductance to- current ratio characteristics and the electrical simulation. The

# "Fig 4" Schematics of a two-stage operational amplifier

Synthesis of a two-stage operational amplifier is shown in order to demonstrate the capabilities of the methodology. The paper describes simulated annealing process in which metal cools and freezes into a minimum energy crystalline structure. This algorithm employs a random search which does not only accept solutions that decrease the objective cost function fc but also some changes that increase it. This paper exploits different transistor lengths and provides an acceptable solution in a reasonable CPU time. It is a simple sizing method based on transistor inversion coefficient which is calculated by curve gm/ID versus I.

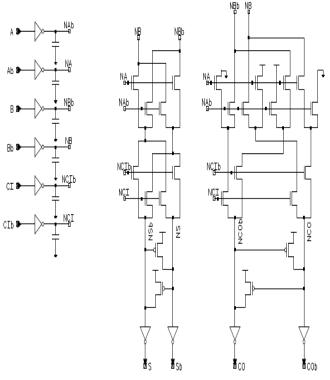

#### 2.3. BASED ON GENETIC ALGORITHM

In this paper, transistor sizing is very important for determination of the circuit performance. This paper [3] is based on the methodology of genetic algorithm for energy consumption optimization. Simulation results in this paper show that, compared with the hybrid tree structure, the GA transistor sizing exhibits better simplicity, initial values, independency, optimization parameter independence and short runtime. The average improvement in PDD is 7% for XOR/XNOR circuits and 17% for full adder. In this technique, all the circuits are simulated using Hspice circuit simulated based on two techniques 0.13um and 0.18um based on BS1M3V and TSMC model.

The main objective of annealing and compact model is to minimize the power delay product on the energy consumption. The energy consumption was optimized. The transistor size run time is reduced by using Genetic algorithm in transistor sizing optimization. Finally compared

"Fig 5" The New HPSC Full adder

to the hybrid tree structure algorithm, the PDP characteristics are improved by 7% in XOR/XNOR circuit and 17% in full adder for the supply voltage range of 0.6 to 0.2 V. The saving in PDP increases in the larger circuit.

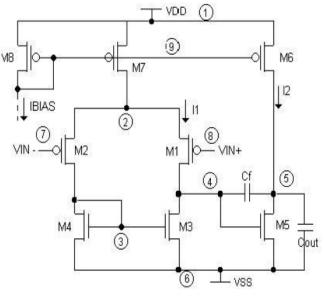

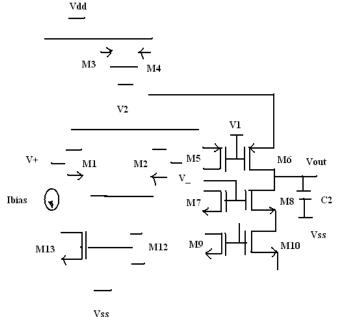

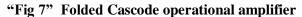

# 2.4. OPTIMIZATION USING GEOMETRIC PROGRAMMING

This paper describes a design of folded cascade operational amplifier with power optimization using geometric programming. The basic idea of the folded-cascode operational amplifier is to apply cascode operational amplifier transistors to the input differential pair. In this study, the main concepts of power optimization using geometric programming are introduced. Geometric Programming, a method for optimizing and automating component and transistor sizing will apply to the power optimization of Folded Cascode operational amplifier. The simulation of the folded cascode circuit is done using TSPICE simulation tool and 0.035  $\mu$ m CMOS technology is

used. Design of the circuit and simulation results are presented demonstrating the amplifier power optimization. In this paper we introduced a new method, geometric programming, for determining the component values and transistor dimensions for CMOS op-amps. The method handles a wide variety of specifications and constraints, is extremely fast, and results in globally optimal designs.

# "Fig 6" Differential amplifier with cascade arrangement

This paper describes geometric programming, for circuit sizing and optimization. Initially our work describes the design of differential amplifier with cascade arrangement and then the design of folded-cascode operational amplifier. The simulation folded cascode op-amp circuit is done using TSPICE simulation tool and the T-spice parameters are mentioned.

Simulated result shows that this op amp exhibits the average power is 1.007X10-13 that is 100 fW or 0.1 nW operating at 100 KHz frequency. The Geometric Programming is successfully applied and the optimized

average power is obtained 9.0658X10-14 that is 90 fW or 0.09 nW operating at 100 KHz frequency.

| S.No | Transistor Sizing                                                     | Algorithm                                            | Circuit                                       | Technology       | Power                        | Run time | No of<br>Transist<br>ors |

|------|-----------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------|------------------------------|----------|--------------------------|

| 1.   | Robert<br>Rogenmoser,<br>Hubert Kaeslin,<br>Tobias Blickle in<br>1996 | Schoastic<br>Monte Carlo<br>and genetic<br>algorithm | NAND3                                         | 1.0µm            | 3.0                          | Less     | 6                        |

|      |                                                                       |                                                      | DFF<br>CPLFA                                  | 1.0µm<br>0.6µm   | 5.8<br>36.7                  |          | 12<br>26                 |

| 2.   | Alessandro Girandi<br>and Sergio Bampi<br>in 2006                     | Annealing<br>and ACM<br>compact<br>model             | OPAMP                                         | 0.35µm           | -                            | More     | 8                        |

| 3.   | M. Grailoo, T.<br>Nikoubin, K. Navi<br>in 2009                        | Genetic<br>algorithm                                 | HPSC Full<br>adder<br>(XOR/XNO<br>R gate)     | 0.13μm<br>0.18μm | 0.406                        | More     | 18                       |

| 4.   | Amol W. Pardhi<br>and Dr.A.Y.<br>Deshmukh in 2012                     | Geometric<br>programming                             | Folded<br>cascode<br>operational<br>amplifier | 0.035μm<br>CMOS  | 9.0658x<br>10 <sup>-14</sup> | Less     | 12                       |

| "Table 1" | Comparison | of different | transistor | sizing       | analog a | nd digital | CMOS c | ircuits |

|-----------|------------|--------------|------------|--------------|----------|------------|--------|---------|

|           |            |              |            | <del>0</del> |          |            |        |         |

### III. CONCLUSION

Transistor sizing is an effective technology for reducing the power, delay in the analog and digital CMOS circuits of an embedded system. In this way different technique such as genetic algorithm, geometric programming, Monte Carlo algorithm are reviewed and compared the performance from the most recent published research work. Different algorithms are discussed to reduce the size of the transistors in which genetic algorithm is more efficient and it leads to better circuit performance in the case of power consumptions. The size of the transistor size is reduced under 180° and further proceeding should be carried our below 100°. By using the analysis of different algorithms the low power circuit can be implemented in embedded system.

### REFERENCES

[1] S.S. Sapatnekar, V.B. Rao, P.M. Vaidya and Sung-Mo Kang, "An exact solution to the transistor sizing problem for CMOS circuits using convex optimization," *Computer*- Aided Design of Integrated Circuits and Systems, IEEE Transactions on, vol.12, no.11, pp.1621-1634, Nov. 1993.

- K. Deb, "An introduction to genetic algorithms," *Sadhana*, Vol.24, Parts 4 & 5, August & October 1999, pp. 293-315.

- [3] Haupt, R.L., Haupt, S.E, 2004, "Practical Genetic Algorithms", *John Willey & Sonc, Inc.*

- [4] Varun Aggarwal and Una-May O'Reilly, "Design of Posynomial Models for Mosfets: Symbolic Regression Using Genetic Algorithms", Genetic Programming: Theory and Practice IV : pp. 219-236, 2006.

- [5] F. Aezinia, A. Afzali-Kusha and C. Lucas, "Optimizing High Speed Flip-Flop Using Genetic Algorithm," *Circuits* and Systems, APCCAS 2006, IEEE Asia Pacific Conference on, pp.1787-1790, 4-7 Dec. 2006.

- [6] Y. Chien-Cheng, "Low-Power Double Edge-Triggered Flip-Flop Circuit Design," *Innovative Computing Information* and Control, 2008, 3rd International Conference on, pp.566, 18-20 June 2008.

- [7] R.A. Thakker, M.S. Baghini and M.B. Patil, "Low-Power Low- Voltage Analog Circuit Design Using Hierarchical Particle Swarm Optimization," VLSI Design 2009, 22nd International Conference on, pp.427-432, 5-9 Jan. 2009.

- [8] M.J.P. Jalali and A. Rezaee, "Power optimization in 70nm technology," *Computer Engineering and Technology* (*ICCET*), 2010 2nd International Conference on, vol.3, pp.V3-136-V3-139, 16-18 April 2010.

- [9] T. Nikoubin, S. Pouri, P. Bahrebar and N. Navi, "A New Transistor Sizing Algorithm for Balanced XOR/XNOR Circuits," CSICC. Faculty of Electronical and Computer Engineering, SBU, Tehran, Iran February 20-22, 2007, [12th International CSI Computer Conference, CSICC 2007, Tehran, Iran] (in Persian).

- [10] T. Nikoubin, P. Bahrebar and N. Navi, "A New Design for XOR/XNOR Circuits, Based on High-Speed and Low-Power Arithmetic Circuits used Signal Processing", *BEC Magn. Iran, vol. 1, pp. 203-209,* [second Broadcast Engineering Conference. IRIB University, Iran, 17-19 November 2007] (in Persian).

- [11] JH Yu, ZG Mao, "A design method in CMOS operational amplifier optimization based on adaptive genetic algorithm", WSEAS Transactions on circuit and systems, vol. 8, pp 548-558,2009.

- [12] Er. Rajni, "Design of High Gain Folded-Cascode Operational Amplifier Using 1.25 um CMOS Technology" International Journal of Scientific & Engineering Research Volume 2, Issue 11, November-2011